- Cadence vlsi design tool how to#

- Cadence vlsi design tool software#

- Cadence vlsi design tool code#

- Cadence vlsi design tool license#

- Cadence vlsi design tool download#

If you have any experience working on these tools, let’s discuss in the comment. I have listed some of the popular VLSI EDA tools.

Cadence vlsi design tool download#

Related Read: Free Download Electrical CAD (ECAD) Softwares Having a basic coding knowledge of C/C++, embedded C programming, Matlab/Simulink and scripting languages (like TCL, Perl) will be useful for learning VLSI designing.

HDL consists of different languages such as Verilog, VHDL, and SystemVerilog. Which Programming Language is Used in VLSI?įor VSLI design, hardware description language (HDL) is used.

Cadence vlsi design tool software#

These expensive in cost.įor learning purposes, you can use open-source software tools like Electric, Alliance, Glade.

Cadence vlsi design tool license#

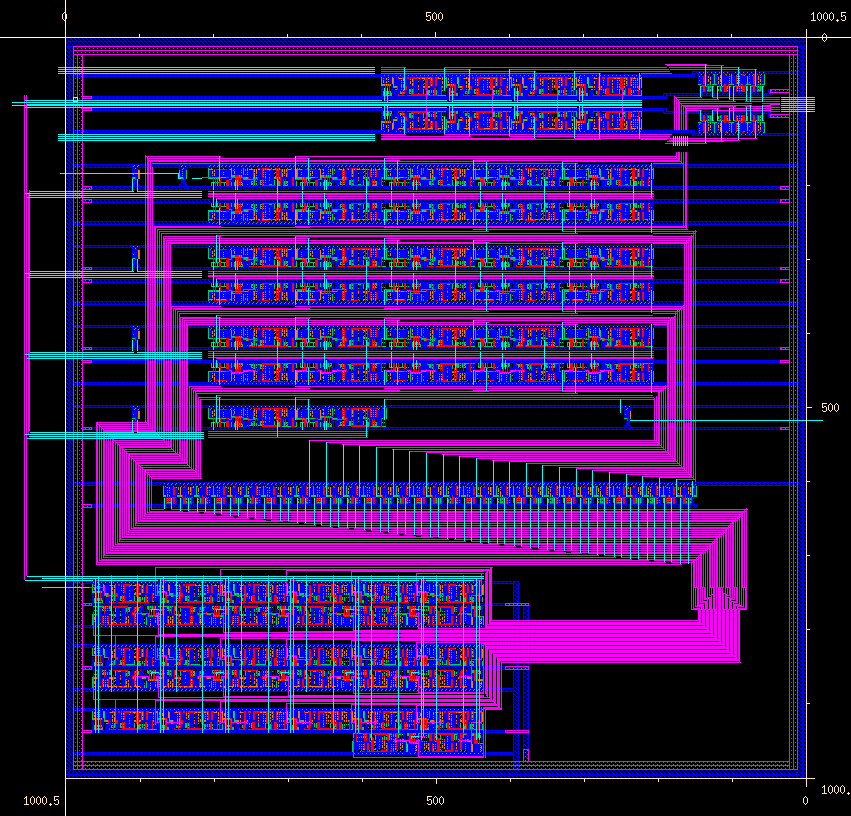

To use these software’s you have to purchase the license as they are not open source. Answer: The rationale behind the question makes no sense.Cadence tools are high end used mostly by Educational and multinational firms.These organisation pays Cadence to obtain these software licensing.If you are using these tools. ECE 6130/4130 (Advanced VLSI Systems): The Virtuoso schematic/layout editors and Diva/Calibre DRC/LVS/Extraction tools are used in this course to teach students advances concepts of digital system design using the NCSU Design Kit. In the industrial environment, Cadence virtuoso, Synopsys, and Mentor Graphics are mostly used. The Cadence tools in this course introduces students to the basic VLSI design skills. If you have any doubts related to this articletop 09 EDA tools for VLSI chip design, then comment below. I hope this article may help you all a lot. These are the top 09 EDA tools for VLSI chip design. Its uniqueness stems from the delicate balance that it maintains between theoretical coverage and hands-on experience, and between topic broadness and information. And some are licensed based for which you have to pay. Cadence is a very popular tool for VLSI chip design. 'The Arm education kit, available through the Cadence University Program, is a unique offering that caters to the needs of advanced undergraduate students in the field of VLSI design. Some of these tools are open-source and available for free. 1.2 Cadence User Interface In Cadence the user interface is graphicand based on windows,forms, and menues.

Cadence vlsi design tool how to#

List of Electronic Design Automation (EDA) tools: verilog simulation cadence cadence digital flow for simulation of verilog RTL code.here explained how to simulate verilog design using cadance simulation. CADENCE DESIGN TOOLS This chapter will give an overview of the user interface supplied by DFW and present some of the Cadence tools that will be used. If you are from India, there are many top institutes that offer VLSI course. There are multiple EDA tools available in the market. It uses multiple features like logical design, circuit schematic design, layout generation, design simulation and may more features for VSLI design. EDA tools help to create multiple types of electronic circuits like an integrated circuit (IC), printed circuit board (PCB) and system on chip (SoC). COUPON: RENT Digital VLSI Chip Design with Cadence and Synopsys CAD Tools 1st edition (9780321547996) and save up to 80 on textbook rentals and 90 on used textbooks. It is a software tool used to design the electronic circuit. EDA is also known as Electronic Computer-Aided Design (ECAD).

Cadence vlsi design tool code#

The synthesis team performs synthesis on RTL code with the standard cell libraries and constraints and converts the RTL code into the gate-level netlist based on available standard cells. Let's briefly see the content of these files. These files come from the synthesis team.

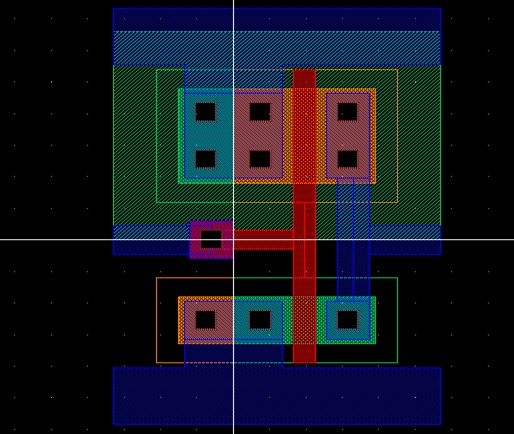

In the set input files, the first set is design-related files which contain Gate level netlist file and design constraint files. Figure-1 shows the list of inputs required for physical design and categories the mandatory and optional inputs.

EDA tool for VLSI with License: In the industrial environment, Cadence virtuoso, Synopsys, and Mentor Graphics are mostly used. And some are licensed based for which you have to pay. Some inputs are mandatory in all the cases but some are required for a specific purpose. Some of these tools are open-source and available for free. Inputs required for physical design can be categories broadly into two types. In the previous article, we have discussed the physical design flow and sanity checks before the floorplan.

In this article, we will discuss what are the inputs required to begin the physical design.

0 kommentar(er)

0 kommentar(er)